时钟

参考链接

【STM32】时钟_stm32f405 定时器时钟-CSDN博客

时钟相关缩写

| 缩写 | 英文全称 | 中文说明 |

|---|---|---|

| RCC | Reset and Clock Control | 复位与时钟控制 |

| RTC | Real-Time Clock | 实时时钟 |

| BKP | Backup Registers | 备份寄存器 |

| PWR | Power Control | 电源控制 |

| HCLK | AHB Clock | AHB总线时钟 |

| USBCLK | USB Clock | USB时钟 |

| LSCO | Low Speed Clock Output | 低速时钟输出 |

| MSI | Multi-Speed Internal Clock | 多速内部时钟 |

| CSS | Clock Security System | 时钟安全系统 |

| LPTIM | Low Power Timer | 低功耗定时器 |

| WDG | Watchdog Timer | 看门狗定时器 |

| HSE | High-Speed External Clock | 高速外部时钟 |

| HSI | High-Speed Internal Clock | 高速内部时钟 |

| LSE | Low-Speed External Clock | 低速外部时钟 |

| LSI | Low-Speed Internal Clock | 低速内部时钟 |

| PLL | Phase-Locked Loop | 锁相环 |

| SYSCLK | System Clock | 系统时钟 |

| PCLK | Peripheral Clock | 外设时钟 |

| APB | Advanced Peripheral Bus | 高级外设总线 |

| AHB | Advanced High-performance Bus | 高级高性能总线 |

概念

首先我们得搞清楚几个概念:

- 时钟:单片机的心脏,所有外设的运作都需要时钟供能。

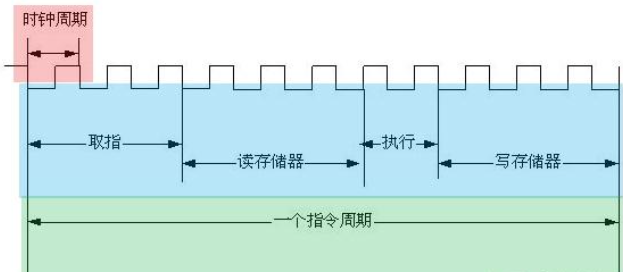

- 时钟周期:又称为振荡周期,可以简单理解为传输一个 0 or 1 所需要的时间。

- 指令周期:执行一条指令(如:MOV A,#34H)所需的时间。对于不同类型的指令,指令周期长度可能会不同。

- 机器周期:执行一个动作的时间周期。如:执行一个指令需要 “取指令并驿码”、"执行操作数"两个动作。

以上三个周期的关系图如下:

简单来说,时钟是具有周期性的脉冲信号,最常用的是占空比50%的方波

时钟是单片机的脉搏,搞懂时钟走向及关系,对单片机使用至关重要!

时钟树

可以使用三种不同的时钟源来驱动系统时钟:

- HSI振荡器时钟

- HSE振荡器时钟

- 主PLL(PLL)时钟

器件有以下两个次级时钟源:

- 低速内部 RC (LSI RC),该 RC 用于驱动独立看门狗,也可选择提供给 RTC 用于停机/待机模式下的自动唤醒。

- 低速外部晶振(LSE 晶振),用于驱动 RTC 时钟 (RTCCLK)对于每个时钟源来说,在未使用时都可单独打开或者关闭,以降低功耗

时钟源:

| 时钟源名称 | 频率 | 材料 | 用途 |

|---|---|---|---|

| 高速外部振荡器(HSE) | 4~16MHz | 晶体/陶瓷 | SYSCLK/RTC |

| 低速外部振荡器(LSE) | 32.768KH Z | 晶体/陶瓷 | RTC(实时时钟) |

| 高速内部振荡器(HSI) | 8MHz | RC | SYSCLK |

| 低速内部振荡器(LSI) | 40KHz | RC | RTC/IWDG |

[!TIP]

H:high L:low S:speed I:internal E:external

时钟控制器为应用带来了高度的灵活性,用户在运行内核和外设时可选择使用外部晶振或者使用振荡器,既可采用最高的频率,也可为以太网、USB OTG FS 以及 HS、I2S 和 SDIO等需要特定时钟的外设保证合适的频率。

可通过多个预分频器配置 ==AHB 频率==、==高速 APB (APB2)== 和==低速 APB (APB1)==。

- AHB 域的最大频率为 168 MHz。

- 高速 APB2 域的最大允许频率为 84 MHz。

- 低速 APB1 域的最大允许频率为 42 MHz。

除以下时钟外,所有外设时钟均由系统时钟 (SYSCLK) 提供:

-

来自于特定 PLL 输出 (PLL48CLK) 的 USB OTG FS 时钟 (48 MHz)、基于模拟技术的随机数发生器 (RNG) 时钟 (<=48 MHz) 和 SDIO 时钟 (<=48 MHz)。

-

I2S 时钟

STM32F405xx/07xx 和 STM32F415xx/17xx 的定时器时钟频率由硬件自动设置。分为两种情况:

- 如果 APB 预分频器为 1,定时器时钟频率等于 APB 域的频率。

- 否则,等于 APB 域的频率的两倍 (×2)。

配置时钟:==使能时钟 > 调用SystemInit()函数(在system_stm32xxx.c中定义)> 选择时钟源,配置PLL > 选择系统时钟源,配置总线分频器 > 配置扩展外设时钟==

代码

1 |

|

HSE时钟

高速外部时钟信号(HSE)有两个时钟源

- HSE外部用户时钟

- HSE外部晶振/陶瓷谐振器

外部源(HSE 旁路)

在此模式下,必须提供外部时钟源。此模式通过将 RCC 时钟控制寄存器 (RCC_CR) 中的HSEBYP 和 HSEON 位置 1 进行选择。必须使用占空比约为 50% 的外部时钟信号(方波、正弦波或三角波)来驱动 OSC_IN 引脚,同时 OSC_OUT 引脚应保持为高阻态 (hi-Z)。

外部晶振/ 陶瓷谐振器(HSE 晶振)

HSE 的特点是精度非常高。

RCC 时钟控制寄存器 (RCC_CR) 中的 HSERDY 标志指示高速外部振荡器是否稳定。在启动时,硬件将此位置 1 后,此时钟才可以使用。如在 RCC 时钟中断寄存器 (RCC_CIR) 中使能中断,则可产生中断。

HSE 晶振可通过 RCC 时钟控制寄存器 (RCC_CR) 中的 HSEON 位打开或关闭。

负载电容(起振电容)必须==尽可能的靠近振荡器==/谐振器的引脚,以尽量减小输出失真和起振稳定时间,负载电容值必须根据所选振荡器的不同做适当的调整

[!TIP]

晶振(晶体振荡器):

利用石英晶体的压电效应来生成稳定的振荡频率。

主要用于为电路提供一个高精度的时钟信号,如微控制器、电脑等。

协振器(谐振器):

可以是LC电路或陶瓷谐振器,依靠电感、电容或物理振动来产生共振。

它与晶振相似,可以用于生成振荡信号,但通常精度较低,稳定性也比晶振差。

HSI时钟

HSI 时钟信号由内部 16 MHz RC(电阻电容) 振荡器生成,可直接用作系统时钟,或者用作 PLL 输入。HSI RC 振荡器的优点是成本较低(无需使用外部组件)。此外,其启动速度也要比 HSE 晶振快,但即使校准后,其精度也不及外部晶振或陶瓷谐振器。

STM32中的HSI(High-Speed Internal)内部时钟是指芯片内部产生的高速时钟信号。HSI是STM32微控制器系列的一部分,通常用作系统时钟的一个选项。HSI时钟信号由芯片内部的振荡器产生,其频率通常为16 MHz(具体数值可能因STM32系列而异)。

HSI时钟通常用于以下用途:

-

启动和初始化:在STM32芯片上电后,通常会首先使用HSI时钟来启动和初始化系统,然后再切换到外部时钟源(如HSE)。

-

低功耗模式:当系统需要进入低功耗模式时,可以选择将时钟切换回HSI,以减少功耗。

-

内部模块时钟:一些内部模块,如看门狗定时器(WDT)和RTC(实时时钟),可能使用HSI时钟。

-

频率可选性:HSI时钟通常具有多个频率选项,可以根据应用的需求进行配置。

需要注意的是,HSI时钟通常比外部时钟源(如HSE,高速外部)的精度和稳定性较差,因此在要求高精度的应用中,通常会选择外部时钟源作为系统时钟。但在许多应用中,HSI时钟足够满足要求,并且可以在降低功耗或简化设计时提供灵活性。

PLL

F4芯片有两个PLL:

-

主PLL由HSE和HSI振荡器提供时钟信号,并具有两个不同的输出时钟

-

用于生成告诉系统时钟(最高达168MHz)

-

输出用于生成USB OTG FS的时钟(48Mhz)、随机数发生器的时钟(<=48MHz)和SDIO时钟(<=48MHz)

-

-

专用PLL(PLLI2S)用于生成精确时钟,从而在I2S接口实现高品质的音频性能

由于在 PLL 使能后主 PLL 配置参数便不可更改,所以建议先对 PLL 进行配置,然后再使能(选择 HSI 或 HSE 振荡器作为 PLL 时钟源,并配置分频系数 M、N、P 和 Q)。

PLLI2S 使用与 PLL 相同的输入时钟(PLLM[5:0] 和 PLLSRC 位为两个 PLL 所共用)。但是,PLLI2S 具有专门的使能/禁止和分频系数(N 和 R)配置位。在 PLLI2S 使能后,配置参数便不能更改。

当进入停机和待机模式后,两个 PLL 将由硬件禁止;如将 HSE 或 PLL(由 HSE 提供时钟信号)用作系统时钟,则在 HSE 发生故障时,两个 PLL 也将由硬件禁止。RCC PLL 配置寄存器 (RCC_PLLCFGR) 和RCC 时钟配置寄存器 (RCC_CFGR) 可分别用于配置 PLL 和 PLLI2S。

PLL 主要用于以下几个方面:

-

时钟生成和同步:PLL 可以用于生成一个稳定的时钟信号,将其锁定到外部参考时钟,从而使系统中的各个部分能够以相同的时间基准运行。这在数字系统、通信系统、计算机系统和许多其他应用中非常重要。

-

频率合成:PLL 可以将一个低频率的参考信号合成为高频率的输出信号。这对于需要高频率时钟信号的应用非常有用,如通信设备、射频电路和数字信号处理器。

-

时钟恢复:在通信系统中,接收到的信号通常会被传输过程中的噪声和时延所影响。PLL 可以用于从接收到的信号中恢复出其原始时钟,以便正确解码和处理数据。

-

频率调制和解调:在调制和解调过程中,PLL 可以用于调整信号的频率,以便将信息嵌入到载波中(调制)或从载波中提取出信息(解调)。

-

时钟多路复用:PLL 可以用于将多个输入时钟信号多路复用到一个输出时钟上,以满足复杂系统中的时钟要求。

-

频率锁定:PLL 可以用于锁定一个振荡器或电路的输出频率到一个稳定的参考频率,以确保输出频率与所需频率匹配。

LSE时钟

LSE 晶振是 32.768 kHz 低速外部 (LSE) 晶振或陶瓷谐振器,可作为实时时钟外设 (RTC) 的时钟源来提供时钟/日历或其它定时功能,具有功耗低且精度高的优点。

LSE 晶振通过 RCC 备份域控制寄存器 (RCC_BDCR) 中的 LSEON 位打开和关闭。

RCC 备份域控制寄存器 (RCC_BDCR) 中的 LSERDY 标志指示 LSE 晶振是否稳定。在启动时,硬件将此位置 1 后,LSE 晶振输出时钟信号才可以使用。如在 RCC 时钟中断寄存器(RCC_CIR) 中使能中断,则可产生中断。

外部源(LSE旁路)

在此模式下,必须提供外部时钟源,最高频率不超过 1 MHz。此模式通过将 RCC 备份域控制寄存器 (RCC_BDCR) 中的 LSEBYP 和 LSEON 位置 1 进行选择。必须使用占空比约为 50%的外部时钟信号(方波、正弦波或三角波)来驱动 OSC32_IN 引脚,同时 OSC32_OUT 引脚应保持为高阻态 (Hi-Z)。

LSI

LSI RC 可作为低功耗时钟源在停机和待机模式下保持运行,供独立看门狗 (IWDG) 和自动唤醒单元 (AWU) 使用。时钟频率在 32 kHz 左右。

LSI RC 可通过 RCC 时钟控制和状态寄存器 (RCC_CSR) 中的 LSION 位打开或关闭。

RCC 时钟控制和状态寄存器 (RCC_CSR) 中的 LSIRDY 标志指示低速内部振荡器是否稳定。在启动时,硬件将此位置 1 后,此时钟才可以使用。如在 RCC 时钟中断寄存器 (RCC_CIR) 中使能中断,则可产生中断。

SYSCLK

在系统复位后,默认系统时钟为 HSI。在直接使用 HSI 或者通过 PLL 使用时钟源来作为系统时钟时,该时钟源无法停止。

只有在目标时钟源已就绪时(时钟在启动延迟或 PLL 锁相后稳定时),才可从一个时钟源切换到另一个。如果选择尚未就绪的时钟源,则切换在该时钟源就绪时才会进行。RCC 时钟控制寄存器 (RCC_CR) 中的状态位指示哪个(些)时钟已就绪,以及当前哪个时钟正充当系统时钟。

SYSTICK

SysTick(滴答)定时器被捆绑在NVIC中,用于产生SYSTICK异常(异常号:15)。

在以前,大多操作系统需要一个硬件定时器来产生操作系统需要的滴答中断,作为整个系统的==时基==。

例如,为多个任务许以不同数目的时间片,确保没有一个任务能霸占系统;或者把每个定时器周期的某个时间范围赐予特定的任务等,还有操作系统提供的各种定时功能,都与这个滴答定时器有关。因此,需要一个定时器来产生周期性的中断,而且最好还让用户程序不能随意访问它的寄存器,以维持操作系统“心跳”的节律。

Systick定时器就是系统滴答定时器,一个24 位的倒计数定时器,计到0 时,将从RELOAD 寄存器中自动重装载定时初值。只要不把它在SysTick 控制及状态寄存器中的使能位清除,就永不停息,即使在睡眠模式下也能工作。